RK3588J External WiFi 5 Deep Dive: BL-M8822CP1 Hardware Design Practice

In high-performance embedded system design, pairing the Rockchip RK3588J with a WiFi 5 module is the standard solution for achieving high-speed networking. This article provides an in-depth analysis of hardware connectivity and design essentials based on the actual schematic of the B-Link BL-M8822CP1.

The core of the BL-M8822CP1 module features the Realtek RTL8822CE high-performance chip. This chip is a highly integrated single-chip solution supporting 2T2R MIMO technology and is compatible with the 802.11ac Wave 2 standard. It integrates RF, baseband, and PHY layers, supporting 2.4GHz/5GHz dual-band communication with a theoretical WiFi rate of up to 867Mbps. Additionally, the chip integrates a Bluetooth 5.0 controller supporting various low-power modes, providing an extremely stable wireless expansion foundation for the RK3588J.

1. Core Interface and Power Filtering Design

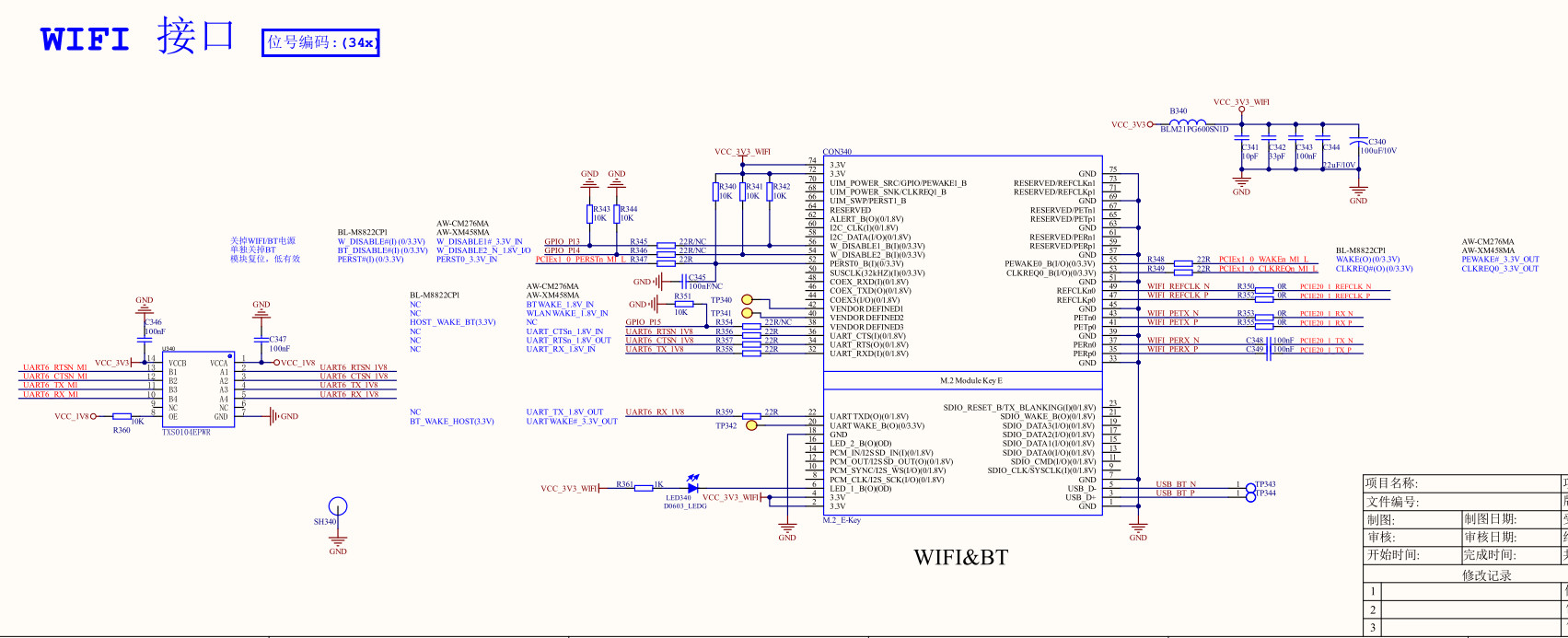

Based on schematic analysis, the BL-M8822CP1 utilizes a standard M.2 Key E interface. Because the RTL8822CE exhibits significant current fluctuations during high-speed transmission in the 5GHz band, power purity directly affects the EVM (Error Vector Magnitude) indicators.

●Multi-stage Filtering: The schematic uses a B340 magnetic bead (BLM21PG600SN1D) on the VCC_3V3_WIFI line to isolate system noise.

●Capacitor Array: The backend utilizes a parallel combination of 100uF + 22uF large capacitors for voltage stabilization, supplemented by 100nF, 33pF, and 10pF small capacitors to filter high-frequency noise across different bands. This "large for energy storage, small for noise suppression" combination is key to ensuring the module does not drop connections under high loads.

Figure 1: RK3588 Connection to M.2 WiFi Module

2. PCIe 2.0 and USB Signal Links

High-speed communication between the RK3588J and the module relies primarily on the PCIe bus (WiFi) and the USB bus (Bluetooth).

●PCIe Differential Pairs: The WIFI_PETX/RX links must strictly maintain a 100Ω differential impedance. The design includes 100nF AC coupling capacitors (C348/C349) connected in series on the TX transmitter and reference clock lines to prevent DC bias interference and protect the SoC interface.

●Bluetooth Bus: The Bluetooth portion utilizes the USB 2.0 protocol, where the differential signals USB_BT_N/P should have an impedance controlled at 90Ω.

3. Practical Pitfalls: Level Shifting and Signal Matching

The schematic features a TXS0104EPWR (U340) bidirectional level shifter chip. This is necessary because the RK3588J UART control level (typically 1.8V) does not match the module level (3.3V); direct interconnection would lead to system instability.

Weathink, a professional solution provider, emphasizes the following details for industrial-grade projects:

●Reset Logic: The PERST# (Reset) signal should align with the SoC power-on sequence. It is recommended to add a software delay of over 100ms to pull the signal high only after the power supply has stabilized.

●RF Routing: RF traces near the M.2 interface should maintain a complete reference ground plane. Crossing split planes is strictly prohibited to reduce return loss and improve wall-penetration performance.

4. Software Adaptation and Status Monitoring

Once hardware connections are complete, the RK3588J requires the configuration of corresponding PCIe nodes in the DTS (Device Tree Source) and the loading of the RTL8822CE firmware. Furthermore, the LED340 indicator (connected to PIN 2/6) provides a visual hardware "heartbeat," making it easy to determine if the module has initialized successfully during the debugging phase.

5. Summary

A design based on the RK3588J and BL-M8822CP1 is more than just physical pin connections; it requires comprehensive control over power stability, impedance matching, and logic levels. For stability requirements in complex electromagnetic environments, Weathink suggests performing a full Signal Integrity (SI) review early in the design phase to shorten the product development cycle.