Implementing High-Perf Dual-Channel LVDS via RK3588J & GM8775C

Preface

In the fields of industrial control, automotive displays, and medical devices, the Rockchip RK3588J has become the preferred high-performance domestic platform due to its powerful 8K computing capability and industrial-grade wide-temperature characteristics. However, the RK3588J primarily provides native MIPI DSI, HDMI, or DP outputs. How can stable, low-latency signal conversion be achieved when facing large-sized, high-resolution industrial-grade LVDS LCD screens?

Based on a typical hardware design from Weathink, this article provides a deep dive into the core technology of using the GM8775C bridge chip to implement dual-channel LVDS displays on the RK3588J platform.

1. Solution Architecture: MIPI DSI to Dual-Channel LVDS

Core SoC: RK3588J The RK3588J features four MIPI D-PHY lanes, with a single lane supporting bandwidth up to 4.5Gbps. In industrial scenarios, its multi-core architecture easily handles complex graphics rendering, though physical interface matching requires a bridge chip.

Bridge Hub: GM8775C The GM8775C is a low-power, high-performance MIPI-to-LVDS converter:

Input: Receives 4-lane MIPI signals from the RK3588J.

Output: Supports single/dual-channel LVDS output with resolutions up to 1080P@60Hz.

Features: An integrated PLL ensures precise frequency locking for image synchronization during large-scale data transmission.

2. Analysis of Key Schematic Design Points

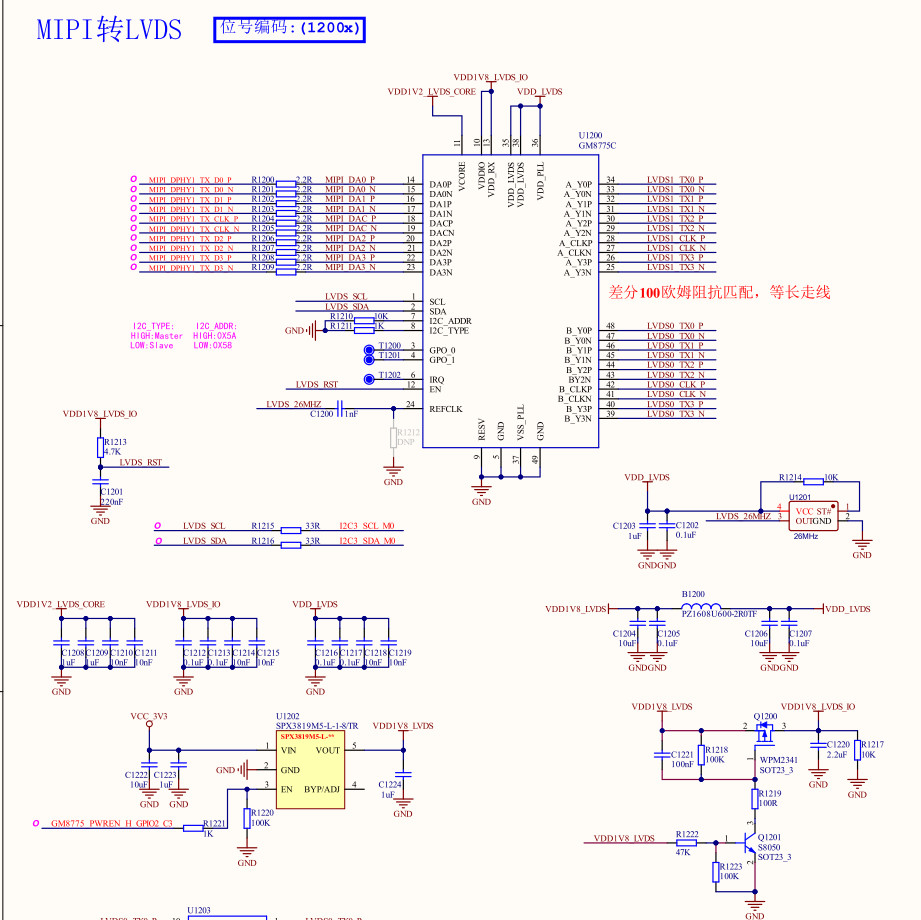

Referring to Weathink’s actual schematic (designators: 1200x), the following elements must be strictly controlled during the circuit design phase:

2.1 Impedance Matching and Length Tuning for High-Speed Signals

MIPI signals from the RK3588J are connected to the GM8775C via R1200-R1209 (2.2Ω) matching resistors.

Key Point: Since both MIPI and LVDS are high-speed differential signals, PCB routing must strictly maintain a 100Ω differential impedance. The schematic specifically notes "100Ω differential impedance matching and equal-length routing," which is critical for avoiding phase shifts and eliminating display ripples.

Figure 1 Schematic diagram of RK3588J connected to GM8775C

2.2 Multi-Stage Power Decoupling Design

To ensure display clarity, the GM8775C power system is rigorously designed:

Independent Power Rails: VCORE (1.2V), VDDIO (1.8V), and VDD_LVDS are supplied independently.

Filter Array: A dense capacitor array (C1208-C1219, ranging from 1uF + 0.1uF + 10nF) effectively covers high, medium, and low-frequency interference to reduce clock jitter.

2.3 External Clock and Reset Logic

Active Crystal: U1201 outputs a stable 26MHz clock signal (LVDS_26MHZ) as the reference frequency for video decoding.

Reset Strategy: Controlled by the LVDS_RST signal and a power-on sequence circuit, ensuring the GM8775C enters the correct standby initialization state after the RK3588J system boots.

2.4 I2C Control Link

Via LVDS_SCL and LVDS_SDA (connected to Pins 1 & 2 of U1200), the RK3588J master controller can dynamically configure the GM8775C for modes such as single/dual-channel selection and timing adjustments.

3. Software Debugging and Driver Essentials

In the Weathink development environment, engineers typically complete the following:

DTS (Device Tree Source) Configuration: Define the MIPI node's output clock frequency, lane count, and VESA/JEIDA formats.

Bridge Driver Adaptation: Call the GM8775C initialization sequence in the kernel. For dual-channel mode, ensure the data distribution logic for Channels A and B is correct.

Timing Fine-Tuning: Adjust H-Blank and V-Blank parameters for specific LVDS panels (e.g., BOE, Innolux) to achieve optimal display results.

Conclusion

By combining the RK3588J with the GM8775C, Weathink has successfully bridged the interface gap between high-performance SoCs and industrial large screens. This solution not only guarantees signal reliability but also serves as a competitive reference for industrial tablets and central control displays amidst the wave of domestic technology substitution.

Weathink Focusing on the application of domestic chips providing full process technical support schematic design to driver optimization.